Cadence embeds AI across chip design tools to tackle trillion-transistor complexity by 2030

7 Sources

7 Sources

[1]

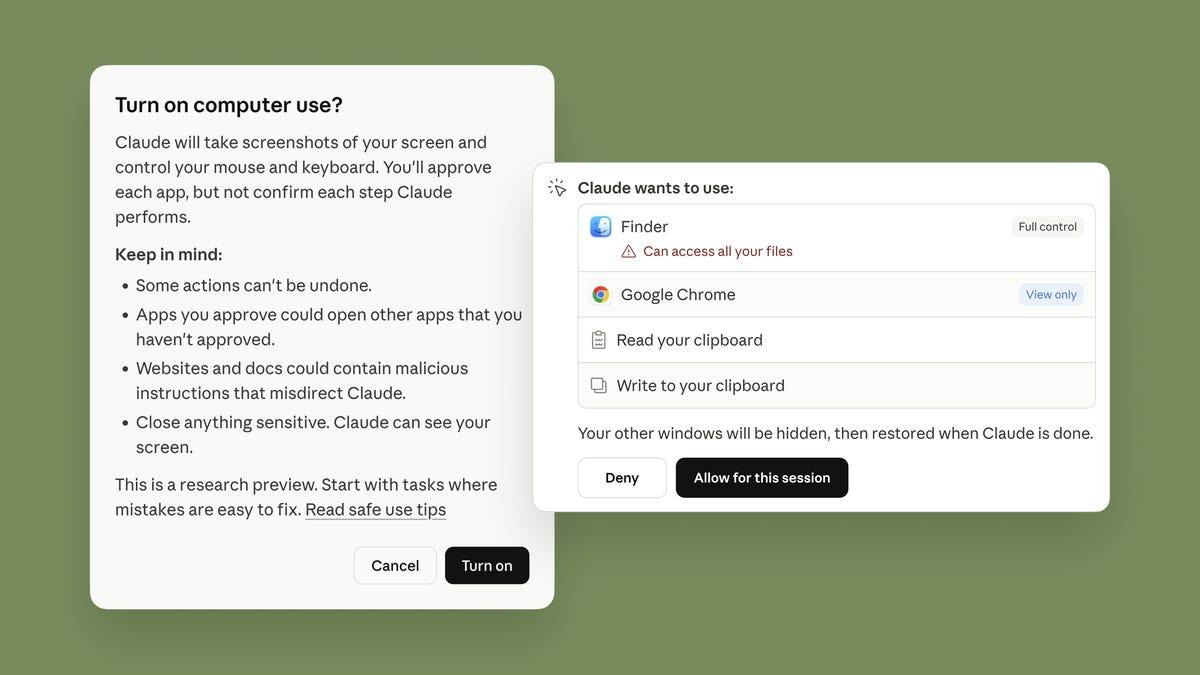

Cadence embeds AI 'super agent' to assist engineers when designing EDA tools -- company aims for 'over a trillion transistors' by 2030, with AI helping to debug and verify complex projects

ChipStack AI Super Agent targets workflow friction amid growing packaging complexity and engineering shortages. "A trillion transistors" sounds like hyperbole, until it's not. Designing today's leading-edge transistors resembles expanding a structure that never stops growing. Chiplets are bolted on as packaging stacks everything vertically, and elements like power delivery and interconnects get re-routed each time footprints change. Eventually, the challenge of designing the actual blueprint is taken over by coordinating everything that connects to it. That coordination is what Cadence is targeting with what it calls its new ChipStack AI Super Agent. Announced February 10, the system embeds an AI-driven assistant across Cadence's electronic and design automation portfolio, with the stated aim of helping engineers design, debug, verify, and sign off complex semiconductor projects more efficiently. "We're easily going to get over a trillion transistors... in the package, by the end of the decade," Cadence Senior Vice President Paul Cunningham said in remarks to Bloomberg. "It's a phenomenal increase in complexity." Cunningham's emphasis on "in the package" is significant because growth to a trillion transistors is not simply about shrinking features at advanced nodes, but assembling multiple dies into unified systems through chiplets, 2.3D interposers, and 3D stacking. And as architectural ambition shifts upward, so too does the burden on design orchestration. EDA has long since automated the mechanics of design, with synthesis, placement, routing, timing analysis, and verification all deeply algorithmic processes that run on large compute clusters. Multi-die packages introduce additional interconnect domains and power islands, push timing closure across die-to-die links, and require thermal modeling across stacked silicon. Verification is therefore no longer isolated to block correctness but extends to system-level interaction between heterogeneous components. Engineers manage these interactions through layered tool flows, scripts, constraints, and sign-off checks, but reports can easily stretch into thousands of lines, and debug cycles can take weeks. Cadence's Super Agent sits above that orchestration layer, acting as what the company describes as a domain-trained AI system built on a "mental model" of chip design rather than a general-purpose large language model. Engineers can interact with the tool stack conversationally, requesting actions without navigating every script or endless menus. "You can chat with all of the Cadence products, and they'll talk back to you," he said. "You don't need to be the ultimate scripting expert. You don't need to know all of the fancy features and tool clicks of our graphic user interfaces. You can just say, 'Hey, look. This is what I want to do.'" The Semiconductor Industry Authority (SIA) projects that the U.S. could face a shortfall of tens of thousands of industry workers by the end of the decade. A meaningful portion of that gap is expected to fall on engineers and technicians with advanced degrees. While expansion in fab capacity under the CHIPS Act -- and corresponding worker shortages -- is what tends to draw the most attention in terms of the semiconductor skills shortage, design expertise is equally constrained. Advanced-node chip design and development demands specialists in physical implementation, verification methodologies, packaging, signal integrity, and system architecture, among other skills. These are roles that require years of specialist training and practical experience, but colleges and universities aren't currently producing graduates at a rate sufficient to match projected demand and expansion. So, while it's all well and good saying "we're going to break the trillion transistors mark," the demands on process coordination increase accordingly as more blocks and interfaces translate into more verification scenarios and failure modes. Without significant changes in workflow, the same design processes will demand more and more engineering hours that will be difficult, if not impossible, to fill. Cadence claims the Super Agent can deliver productivity improvements of up to ten times in certain tasks, a figure that likely reflects targeted gains in repetitive, report-heavy processes. Even so, incremental reductions in iteration time can easily compound across long design schedules and go a long way towards accelerating development cycles. Generative AI has also brought uncertainty to many software categories, raising questions around whether generalized models could abstract away from specialized tools. EDA vendors operate in a tightly constrained market governed by the likes of foundry process design kits and sign-off criteria. Here, things like timing analyzers and physical verification tools aren't easily displaced by general-purpose models. But vulnerabilities do exist: For decades, using EDA tools has required fluency in scripting, flow configuration, and the idiosyncrasies of specific vendor ecosystems. That friction has also been part of what keeps customers embedded. If an external AI assistant could sit on top of those tools and translate intent into tool commands, the interface layer would begin to loosen. By embedding a domain-trained model inside its own stack, Cadence ensures that the conversational interface is part of the platform rather than one of said overlays. This 'Super Agent' doesn't replace timing engines or verification tools, but rather, it sits between the engineer and those tools, interpreting intent and mapping it onto validated flows within the Cadence ecosystem. As architectures fragment into chiplets and stacked dies, constraints are only going to grow, and an assistant that can interpret a designer's request and translate it into correctly sequenced tool operations might reduce misconfiguration and shorten debug cycles. Cadence isn't alone here. Synopsys and others are known to be pursuing similar AI-assisted layers across their portfolios, folding them into tool stacks as a way to reduce coordination overhead. If Cadence succeeds in doing this in a meaningful way, it changes how teams cope with the kind of scale Cunningham is describing. A trillion transistors in a single package multiplies interfaces, verification, and the number of ways things can fail. More dies equals more cross-domain timing checks. More silicon stacks equal more thermal interactions to model. The coordination workload, as we mentioned earlier, rises alongside that. If the supply of advanced engineers doesn't expand at the same pace, that coordination burden has to be absorbed elsewhere. Either development cycles stretch, or the effective output per engineer increases. Cadence is trying to make the latter happen from inside the toolchain.

[2]

Cadence opens the door to chips designed for AI by AI

Nvidia, Qualcomm, and Altera among the first to trial EDA giant's AI chip design agent The idea of machines that can build even better machines sounds like sci-fi, but the concept is becoming a reality as companies like Cadence tap into generative AI to design and validate next-gen processors that also use AI. In the early days of integrated circuits, chips were designed by hand. In the more than half a century since then, semiconductors have grown so complex and their physical features so small that it's only possible to design chips using other chips. Cadence is one of several electronic design automation (EDA) vendors building software for this purpose. Even with this software, the process of designing chips remains time-consuming and error-prone. But with the rise of generative AI, Cadence and others have begun exploring new ways to automate these processes. The latest example of this is Cadence's ChipStack AI "Super" Agent unveiled on Tuesday. The platform is designed to automate tasks like coding designs, running test benches, creating test plans, and orchestrating regression testing in order to debug and resolve issues as they arise. In other words, Cadence has built an AI code assistant for chip design. But while this might just sound like vibe coding for chips, the company insists the agent has sufficient guardrails to limit hallucinations. "By leveraging intelligent agents that autonomously call our underlying tools, we are enabling dramatic productivity gains for our customers in critical design and verification tasks while freeing scarce engineering talent to focus on innovation," Cadence CEO Anirudh Devgan said in a canned statement. And if you're worried about this turning into a Terminator-style Skynet situation, don't. While AI may be used to design better AI chips, it's got a long way left to go to automate the rest of the semiconductor supply chain. ChipStack is actually composed of several sub-agents, or what Cadence is calling virtual engineers, responsible for IP design, verification, sign-off, debugging, and system-on-chip layout. According to Cadence, the agent follows a pipeline that starts by ingesting everything about the part being designed or tested, including specification files and design briefs. These files are used to form a mental model of the chip. The agent then uses this mental model to determine what tests need to be completed and generates the code necessary to do so, while incorporating feedback, presumably from engineers, along the way. From here, the agent may call additional EDA tools, and where failures are reported, the agent automatically generates debug code to resolve issues as they crop up. This capability doesn't appear to be limited to Cadence's own models either. The company says ChipStack can be run on prem using customers' preferred open-weights models or using cloud-based models from the likes of OpenAI. For example, the company suggests that users might use Nvidia's NeMo framework to customize models for their specific design processes. Cadence contends that the agent can boost productivity by up to 10x, a claim that's already caught the attention of several major chip vendors including Qualcomm, Altera, and Nvidia. The latter is perhaps the least surprising. Nvidia has been rather bullish on the prospect of machine learning and generative AI running on its GPUs, naturally, to accelerate all manner of design processes including EDA. Along with EDA, the GPU giant has also developed frameworks, like cuLitho, to accelerate things like computational lithography by simulating the physical properties to design better photomasks for chip production. This tech has already been adopted by major semiconductor equipment vendors and foundries including ASML and TSMC. Cadence is far from the only EDA vendor dipping its toes in the agentic waters. At CES, Nvidia revealed that it was working with Siemens EDA to bring similar agentic functions to its own chip design platform. Meanwhile in December, Nvidia plowed $2 billion into Synopsys, buying common stock to push GPU acceleration across simulation workloads, with EDA among them. ®

[3]

Cadence Touts AI as Way to Speed Design, Cope With Labor Crunch

Cadence built its own AI technology for the Super Agent, creating a mental model based on its knowledge of chip design that it says will not hallucinate or make up false information. Cadence Design Systems Inc. is introducing a new AI tool that can help speed the design of semiconductors, arguing that such technology is necessary to keep up with demand for chips and cope with shortages of skilled labor. A service called the ChipStack AI Super Agent will act as an assistant to engineers who are developing chips, the company said in a statement Tuesday. It will help them design, debug, verify and sign off on final blueprints. Cadence, a top maker of chip-design software, is pushing deeper into AI at a delicate moment. Investors have grown concerned that artificial intelligence will make traditional software obsolete, sending the industry's stocks into a tailspin. Cadence itself saw its shares slide during the past two weeks. But Cadence sees AI as a way to elevate design software, rather than destroy it. AI can help humans manage the staggering complexity of modern chips and escape routine tasks, the company said, bringing as much as a 10-fold increase in productivity. That means employees can focus more on innovating. "We're easily going to get over a trillion transistors in the chip, in the package, by the end of the decade," Cadence Senior Vice President Paul Cunningham said. "It's a phenomenal increase in complexity." Cadence built its own AI technology for the Super Agent because standard large language models weren't up to the challenge. It created a so-called mental model -- based on Cadence's arcane and highly technical knowledge of chip design -- that it says will not hallucinate, or make up false information. Chip development work is already a highly automated process. The job of laying out and verifying new designs has been done by software run on powerful computers for decades. But the sophistication of today's chips is putting a strain on that process. The latest processors now consist of multiple chips combined into one piece of silicon, adding to the complexity -- and increasing the chance that something goes wrong. As a result, even companies with the resources of Nvidia Corp. can't manage more than one design overhaul a year. Tweaks to existing layouts take months to deliver. And errors can cost billions of dollars in lost revenue. The process requires engineers to orchestrate a multitude of operations using various pieces of software. Much of it is routine work that's time-consuming but nonetheless requires an experienced hand. Cadence has made that a friendlier experience, Cunningham said. "You can chat with all of the Cadence products, and they'll talk back to you," he said. "You don't need to be the ultimate scripting expert. You don't need to know all of the fancy features and tool clicks of our graphic user interfaces. You can just say, 'Hey, look. This is what I want to do.'" The AI agent is a step toward creating a virtual engineering assistant -- something that will be needed as the industry deals with a tightening labor supply, Cunningham said. There will be a shortfall of tens of thousands of engineers by the end of the decade, he said, citing statistics from the Semiconductor Industry Association. For now, the AI tool should just help engineers be more efficient. There's nothing coming yet that can design a chip from start to finish, Cunningham said. "Do I believe that it could happen? Yes," he said. "But that's next level -- it's too hard."

[4]

Cadence introduces an AI agent to speed up computer chip design

WASHINGTON, Feb 10 (Reuters) - Cadence Design Systems on Tuesday rolled out a virtual artificial intelligence "agent" to help firms like Nvidia speed up the complex process of designing computer chips, a key front in the technology competition between the U.S. and China. Cadence (CDNS.O), opens new tab sells key tools for designing complex chips with tens of billions of transistors. Before those chips become physical silicon, engineers describe the circuit using a code-like language. The new tool addresses a major industry bottleneck. Chip design is so labor-intensive and costly that engineering teams can spend up to 70% of their time writing and testing code, and analysts say AI-powered productivity boosts are critical for the U.S. to maintain its technological edge. On Tuesday, Cadence introduced a tool called ChipStack AI Super Agent. The agent looks at a chip's design, builds a "mental model" of how the chip is supposed to work, and then can use various Cadence tools to test the design and fix bugs. "Between now and the end of the decade, we are going to transform from being a company where you think of us as licensing new tools to a company to where we rent you virtual engineers," Paul Cunningham, vice president and general manager of research and development at Cadence, said. Cadence said the agent speeds up some tasks by 10 times and is in early use by Nvidia (NVDA.O), opens new tab, Altera and chip startup Tenstorrent, among others. Dave Altavilla, principal analyst of HotTech Vision and Analysis, said such AI productivity tools could be instrumental in the tech competition between the U.S. and China. The U.S. government has restricted the export of advanced chip tools to China, but Chinese companies are developing their own chip design tools and are likely to turbocharge them with AI. "You need that capability to compete," Altavilla said. "They're very smart, and they outnumber (U.S. chip designers) dramatically." Reporting by Stephen Nellis in Washington; Editing by Ethan Smith Our Standards: The Thomson Reuters Trust Principles., opens new tab

[5]

Cadence announces ChipStack 'Super Agent' system for chip design and verification - SiliconANGLE

Cadence announces ChipStack 'Super Agent' system for chip design and verification Integrated circuit and electronic hardware design company Cadence Design Systems Inc. today announced the release of an artificial intelligence "Super Agent" designed to transform front-end silicon design and verification. The company said Cadence ChipStack AI Super Agent will help revolutionize how engineers automate chip design by improving productivity and speeding up coding, design and testbench creation by a factor of 10, as well as creating test plans, orchestrating regression tests, debugging and automatically fixing issues. In an interview with SiliconANGLE, Matt Graham, senior group director, verification software product management, and Kartik Hegde, senior group director of agentic AI, explained that the new agent focuses on the increasingly problematic pain point of verification in chip design. The Super Agent's name, ChipStack, is a product name carryover from when Cadence acquired the company in November 2025. "The ChipStack AI Super Agent is an umbrella, or symphony of agents, like an IP design agent, a verification agent, a system-on-chip integration agent, a debugging agent and more, working together," explained Graham. Verification is the bottleneck for engineers. ChipStack is intended to act as a junior engineer in the face of increasing complexity. "Verification is fundamentally NP complete and grows exponentially," Graham said. "Double the gate count, square the state space. That's the fundamental equation." Inside the agentic core, the mind-in-the-machine, Cadence developed the system to develop a "metal model" that could hold the entire project for engineering teams so that it could interpret all artifacts at once and act like a junior engineer. This allows chip design engineers to input the documentation, block diagrams, waveforms and timing relationships into the agentic loop, have it verified and then ask questions before sending it to automation down the line. Graham framed this problem within the chipmaking industry as having millions of dollars on the line. A single flaw could cost significant amounts if it went into production. Therefore, it needs to be caught early, so testing takes a significant number of resources. The agentic AI system integrates directly with Cadence's optimization AI and AI assistant solutions, which have already been used in more than 1,000 tapeouts to date, including within the company's Cerebrus Intelligent Chip Explorer, as well as JedAI data and AI platform. In an example workflow, a verification engineer takes the agentic system and points it at specifications, the various documents of chip design, drawings, pinouts and so forth and it generates the mental model. Then it generates a test plan, writes and updates test benches, runs simulations, reads logs/waveforms, identifies root causes and proposes fixes. At each stage, the engineer remains in the loop, working alongside it like a senior engineer proposing direction with a junior engineer, the agent, executing actions. "Verification is a deeply natural language reasoning problem and large language models are natural language processing engines," Hegde said. "It's just a perfect fit for the hair-on-fire problem the industry has." Ideally, Cadence wants to build toward a fully autonomous solution that will be able to send out agents and take a prompt, design a chip and do the testing, then provide a fully working chip. "The moonshot is fully autonomous integrated chip design," Graham said, "but we're taking the first steps." As for enterprise readiness, Cadence said the product is available to deploy in the cloud, hybrid and on-premises. Many chip design and fabrication companies are extremely covetous about their intellectual property and do not want it leaked to third parties. Cadence's ChipStack AI Super Agent is currently in early deployment with several chip design and system companies, including Altera Corp., Nvidia Corp. and Tenstorrent Inc.

[6]

Cadence launches AI agent to speed up computer chip design

Cadence Design Systems has introduced a virtual artificial intelligence agent. This tool aims to speed up the complex process of designing computer chips. Companies like Nvidia are already using it. Cadence Design Systems on Tuesday rolled out a virtual artificial intelligence "agent" to help firms like Nvidia speed up the complex process of designing computer chips, a key front in the technology competition between the U.S. and China. Cadence sells key tools for designing complex chips with tens of billions of transistors. Before those chips become physical silicon, engineers describe the circuit using a code-like language. The new tool addresses a major industry bottleneck. Chip design is so labor-intensive and costly that engineering teams can spend up to 70% of their time writing and testing code, and analysts say AI-powered productivity boosts are critical for the U.S. to maintain its technological edge. On Tuesday, Cadence introduced a tool called ChipStack AI Super Agent. The agent looks at a chip's design, builds a "mental model" of how the chip is supposed to work, and then can use various Cadence tools to test the design and fix bugs. "Between now and the end of the decade, we are going to transform from being a company where you think of us as licensing new tools to a company to where we rent you virtual engineers," Paul Cunningham, vice president and general manager of research and development at Cadence, said. Cadence said the agent speeds up some tasks by 10 times and is in early use by Nvidia, Altera and chip startup Tenstorrent, among others. Dave Altavilla, principal analyst of HotTech Vision and Analysis, said such AI productivity tools could be instrumental in the tech competition between the U.S. and China. The U.S. government has restricted the export of advanced chip tools to China, but Chinese companies are developing their own chip design tools and are likely to turbocharge them with AI. "You need that capability to compete," Altavilla said. "They're very smart, and they outnumber (U.S. chip designers) dramatically."

[7]

Cadence introduces an AI agent to speed up computer chip design

WASHINGTON, Feb 10 (Reuters) - Cadence Design Systems on Tuesday rolled out a virtual artificial intelligence "agent" to help firms like Nvidia speed up the complex process of designing computer chips, a key front in the technology competition between the U.S. and China. Cadence sells key tools for designing complex chips with tens of billions of transistors. Before those chips become physical silicon, engineers describe the circuit using a code-like language. The new tool addresses a major industry bottleneck. Chip design is so labor-intensive and costly that engineering teams can spend up to 70% of their time writing and testing code, and analysts say AI-powered productivity boosts are critical for the U.S. to maintain its technological edge. On Tuesday, Cadence introduced a tool called ChipStack AI Super Agent. The agent looks at a chip's design, builds a "mental model" of how the chip is supposed to work, and then can use various Cadence tools to test the design and fix bugs. "Between now and the end of the decade, we are going to transform from being a company where you think of us as licensing new tools to a company to where we rent you virtual engineers," Paul Cunningham, vice president and general manager of research and development at Cadence, said. Cadence said the agent speeds up some tasks by 10 times and is in early use by Nvidia, Altera and chip startup Tenstorrent, among others. Dave Altavilla, principal analyst of HotTech Vision and Analysis, said such AI productivity tools could be instrumental in the tech competition between the U.S. and China. The U.S. government has restricted the export of advanced chip tools to China, but Chinese companies are developing their own chip design tools and are likely to turbocharge them with AI. "You need that capability to compete," Altavilla said. "They're very smart, and they outnumber (U.S. chip designers) dramatically." (Reporting by Stephen Nellis in Washington; Editing by Ethan Smith)

Share

Share

Copy Link

Cadence launched its ChipStack AI Super Agent to help engineers design, debug, and verify chips faster as the industry races toward trillion-transistor packages. With Nvidia, Qualcomm, and Altera already testing the system, the electronic design automation giant claims 10x productivity gains while addressing a looming shortage of tens of thousands of semiconductor workers by decade's end.

Cadence Targets Trillion-Transistor Milestone With AI-Powered Design Assistant

Cadence Design Systems unveiled its ChipStack AI Super Agent on February 10, embedding AI across its electronic design automation (EDA) portfolio to help engineers navigate the escalating complexity of modern semiconductor design

1

. The system addresses a pressing industry challenge: designing chips that will contain over a trillion transistors in a single package by 2030, according to Cadence Senior Vice President Paul Cunningham3

. This exponential growth stems not just from shrinking node sizes but from assembling multiple dies through chiplets, 2.3D interposers, and 3D stacking—architectural shifts that push design orchestration to new limits1

.

Source: The Register

The ChipStack AI Super Agent functions as what Cadence calls a "symphony of agents," including specialized virtual engineers for IP design, verification, system-on-chip integration, and debugging

5

. Engineers can interact conversationally with Cadence's tools without mastering every script or menu. "You can chat with all of the Cadence products, and they'll talk back to you," Cunningham explained. "You don't need to be the ultimate scripting expert. You can just say, 'Hey, look. This is what I want to do'"1

.Boosting Engineer Productivity Amid Growing Labor Shortages

The timing reflects an urgent industry need. The Semiconductor Industry Association projects the U.S. could face a shortfall of tens of thousands of industry workers by the end of the decade, with a meaningful portion falling on engineers with advanced degrees

1

. Chip design teams currently spend up to 70% of their time writing and testing code, creating a major bottleneck4

. Cadence claims the Super Agent can boost engineer productivity by up to 10 times in certain tasks, particularly in repetitive, report-heavy processes2

.Addressing labor shortage concerns, Cunningham stated: "Between now and the end of the decade, we are going to transform from being a company where you think of us as licensing new tools to a company to where we rent you virtual engineers"

4

. This shift toward AI assistant-driven workflows could help bridge the gap as verification grows exponentially more complex. "Double the gate count, square the state space. That's the fundamental equation," explained Matt Graham, Cadence's senior group director of verification software product management5

.How the AI Super Agent Works to Design, Debug, and Verify Chips

Unlike general-purpose large language models, Cadence built the Super Agent using a domain-trained "mental model" based on specialized chip design knowledge

1

. The system ingests specification files and design briefs to understand what tests need completion, then generates code while incorporating engineer feedback2

. When failures surface, the agent automatically generates debug code to resolve issues. Cadence emphasizes this approach minimizes hallucinations—a critical requirement when a single flaw could cost millions if it reaches production5

.The platform supports deployment across cloud, hybrid, and on-premises environments, addressing intellectual property concerns that make chip design companies particularly cautious about third-party exposure

5

. Engineers can run ChipStack using their preferred open-weights models or cloud-based options from providers like OpenAI, with Nvidia's NeMo framework available for customization2

.

Source: SiliconANGLE

Related Stories

Industry Adoption and Competitive Implications for Semiconductor Design

Nvidia, Qualcomm, Altera, and chip startup Tenstorrent are among early adopters testing the system

2

4

. Nvidia's involvement is notable given the company's broader push to accelerate design processes using generative AI running on its GPUs, including frameworks like cuLitho for computational lithography already adopted by ASML and TSMC2

.Cadence isn't alone in pursuing agentic chip design. At CES, Nvidia revealed collaboration with Siemens EDA on similar functions, while in December, Nvidia invested $2 billion in Synopsys to push GPU acceleration across simulation workloads

2

. Dave Altavilla, principal analyst at HotTech Vision and Analysis, framed these AI productivity tools as instrumental in U.S.-China technology competition. With Chinese companies developing their own chip design tools likely to incorporate AI, "You need that capability to compete," Altavilla noted. "They're very smart, and they outnumber U.S. chip designers dramatically"4

.What Comes Next for Autonomous Chip Design

While Cadence envisions fully autonomous chip design as its "moonshot," current capabilities keep engineers firmly in the loop

5

. The agent operates like a junior engineer executing tasks under senior engineer direction, handling routine work that's time-consuming but requires experienced oversight3

. For now, nothing can design a chip from start to finish autonomously. "Do I believe that it could happen? Yes," Cunningham said. "But that's next level—it's too hard"3

. As transistor counts climb and verification demands multiply, the industry will watch whether AI can compress development cycles enough to maintain the pace of innovation even companies with Nvidia's resources currently manage only one major design overhaul annually3

.

Source: ET

References

Summarized by

Navi

[2]

Related Stories

AI Revolutionizes Chip Design: Over 50% of Advanced Silicon Designs Now AI-Assisted

30 Apr 2025•Technology

Cadence Acquires Seattle AI Startup ChipStack to Accelerate Chip Design Automation

10 Nov 2025•Business and Economy

Cadence Unveils Millennium M2000 AI Supercomputer with NVIDIA Blackwell GPUs for Advanced Simulations

09 May 2025•Technology

Recent Highlights

1

Tennessee Teens Sue Elon Musk's xAI Over Grok AI-Generated Child Abuse Images

Policy and Regulation

2

Pentagon designates Palantir Maven AI as core US military system in major defense shift

Technology

3

Supermicro Co-Founder Indicted in $2.5 Billion Nvidia AI Chip Smuggling Scheme to China

Policy and Regulation