AMD Unveils Ambitious AI Plans: EPYC 'Venice' CPU with 256 Cores and Next-Gen AI Solutions for 2026-2027

7 Sources

7 Sources

[1]

AMD unwraps 2027 AI plans: Verano CPU, Instinct MI500X GPU, next-gen AI rack

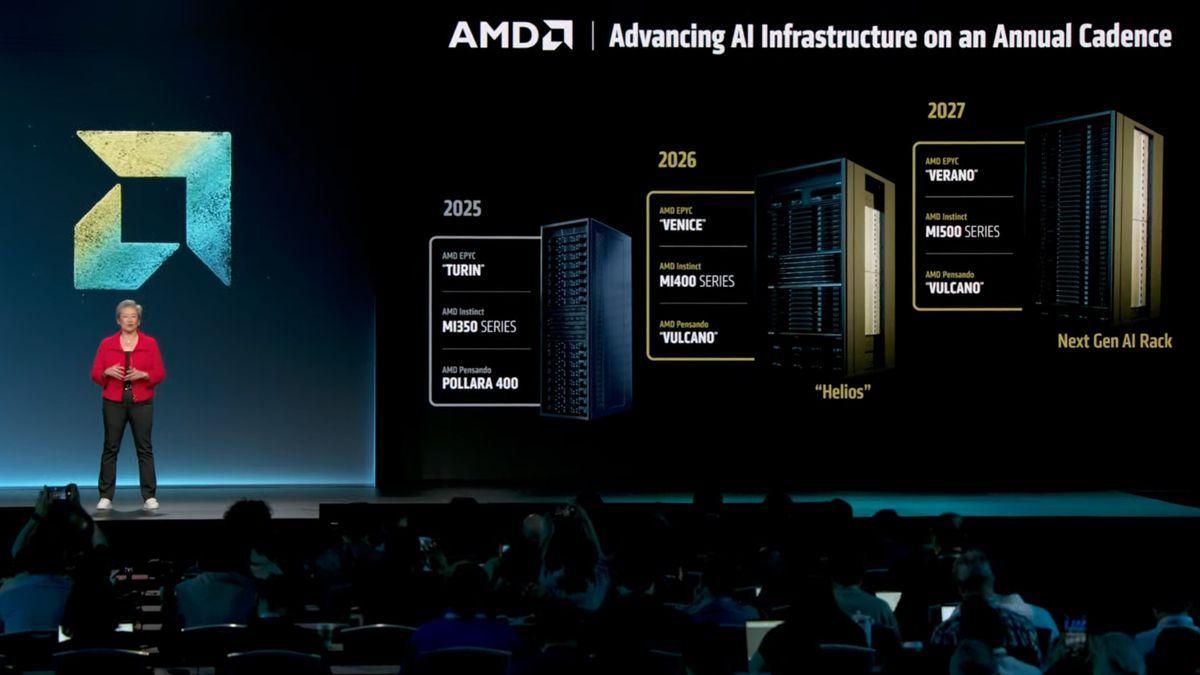

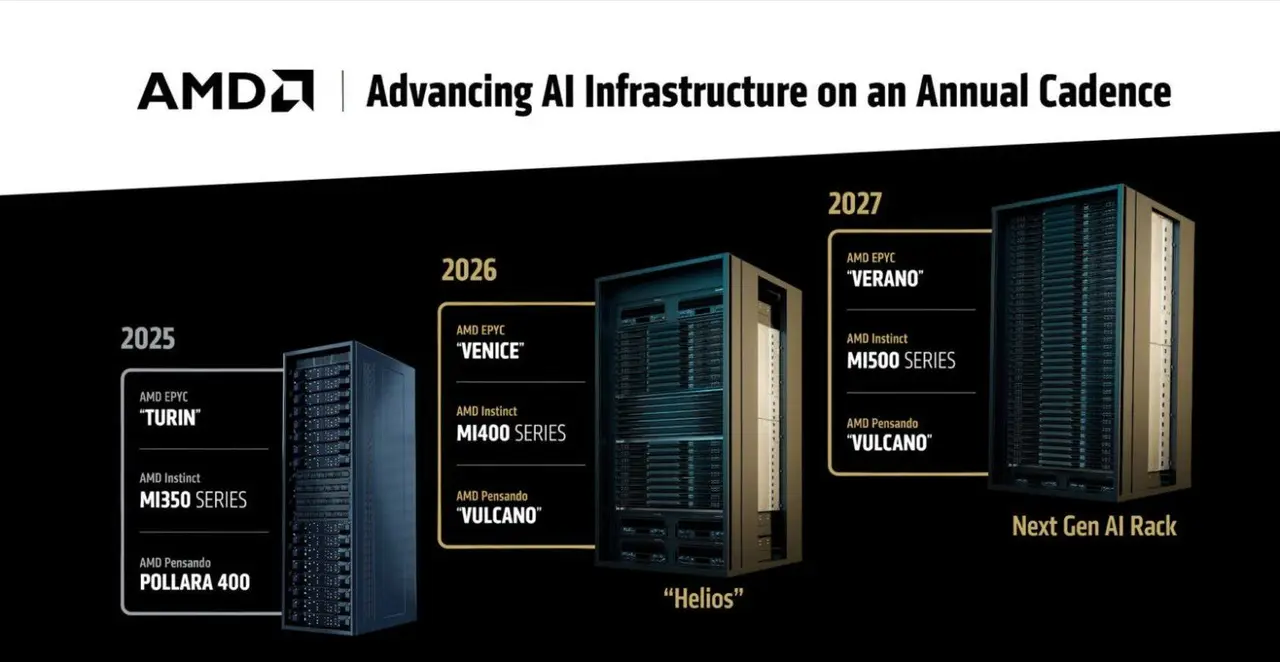

AMD is accelerating its CPU, GPU, and AI rack-scale solutions roadmaps to a yearly cadence, so the company is set to introduce its all-new EPYC 'Verano' CPU, Instinct MI500-series accelerators, and next-generation rack-scale AI solution in 2027, the company revealed at its Advancing AI event. "We are already deep in the development of our 2027 rack-scale solution that will push the envelope even further on performance efficiency and scalability with our next generation Verano CPUs and Instinct MI500X-series GPUs," said Lisa Su, chief executive of AMD, at the event. AMD's 2026 plans for rack-scale AI solutions already look impressive as the company's first in-house designed Helios rack-scale system for AI will be based on AMD's 256-core EPYC 'Venice' processor (expected to deliver a 70% generation-to-generation performance improvement); Instinct MI400X-series accelerators projected to double AI inference performance compared to the Instinct MI355X; and Pensando 'Vulcano' 800 GbE network cards compliant with the UEC 1.0 specification. But the company is set to introduce something even more impressive the following year. That would be AMD's second generation rack-scale system powered by its EPYC 'Verano' processors, Instinct MI500X-series accelerators, and Pensando 'Vulcano' 800 GbE NICs. AMD did not reveal any specifications or performance numbers for its second gen rack-scale solution, EPYC 'Verano' processors, or Instinct MI500X-series GPUs. However, based on a picture the company provided, the post-Helios rack-scale machine will feature more compute blades, thus boosting performance density. This alone points to higher performance and power consumption, which will come handy as this one will have to rival Nvidia's NVL576 'Kyber' system based on 144 Rubin Ultra packages (each packing for reticle-sized compute elements). Production of EPYC 'Verano' CPUs and Instinct MI500X-series accelerators in 2027 align perfectly with TSMC's roll-out of its A16 process technology in late 2026, its first production node to offer backside power delivery, a technology particularly useful for heavy duty datacenter CPUs and GPUs. We do not know whether AMD's 2027 processors and accelerators will rely on TSMC's A16, though it isn't unreasonable to speculate.

[2]

AMD EPYC Venice boasts 256 cores and bandwidth galore -- next-gen server CPUs arrive in 2026

AMD on Thursday revealed some of the first technical details about its next-generation Zen 6-based EPYC 'Venice' processor at its Advancing AI event. The company disclosed that the new server CPU will feature up to 256 cores, which increases the number of cores from the current generation EPYC 'Turin' processor by 33%. But the new microarchitecture and the increased number of cores will not be the only innovation that AMD's 2026 data center CPU will bring. AMD says by packing up to 256 next-generation high-performance Zen 6 cores, the upcoming 6th Generation EPYC 'Venice' CPU will increase performance compared to the existing 5th Generation EPYC 'Turin' 9005-series processor by up to 70%, though the company refrained from elaborating exact workloads it used for comparison. Perhaps more importantly, the new EPYC 'Venice' processor will more than double per-socket memory bandwidth to 1.6 TB/s (up from 614 GB/s in case of the company's existing CPUs) to keep those high-performance Zen 6 cores fed with data all the time. AMD did not disclose how it plans to achieve the 1.6 TB/s bandwidth, though it is reasonable to assume that the new EPYC 'Venice' CPUS will support advanced memory modules like like MR-DIMM and MCR-DIMM. In addition, AMD's 6th Generation EPYC 'Venice' CPU will also double CPU-to-GPU bandwidth, which most likely means that this processor and the company's next-generation Instinct MI400X-series GPUs will use a PCIe 6.0 interface for communication. That would which mean AMD will be able to transfer up to 128 GB (not counting encoding overhead) of data per second in each direction. And with 128 PCIe lanes, the total amount of data that can be moved is likely much higher. "Venice extends our leadership across every dimension that matters in the data center," said Lisa Su, chief executive officer of AMD. "More performance, better efficiency, and outstanding total cost of ownership. It is built on TSMC 2nm process technology and features up to 256 high performance Zen 6 cores. It delivers 70% more compute performance than our current generation EPYC 'Turin' CPU and and to really keep feeding [the Instinct MI400X accelerators] with data at full speed, at even at rack scale, we have doubled both the GPU and the memory bandwidth and optimized Venice to run at higher speeds. [...] We just got 'Venice' back in the labs and it is looking fantastic." AMD's 6th Generation EPYC processors are expected to adopt the all-new SP7 form-factor that is projected to enable the company to place more compute complex dies (CCDs) on the package, increase the number of memory channels, and boost peak power delivery well beyond 700W supported by the SP5 packaging.

[3]

AMD unveils Epyc Venice with 256 cores and 2nm process for next-gen AI and cloud workloads

Serving tech enthusiasts for over 25 years. TechSpot means tech analysis and advice you can trust. What just happened? AMD is preparing to shake up the data center landscape with its forthcoming Epyc Venice processor, a chip that promises to set new standards for performance and scalability in server computing. Announced at the company's recent Advancing AI event, the Venice CPU is built on AMD's next-generation Zen 6 architecture and is slated for release in 2026, targeting the ever-increasing demands of artificial intelligence, cloud computing, and high-performance analytics. Venice makes a dramatic leap in processing power. The chip will support up to 256 Zen 6 cores, a 33 percent increase over the current Epyc Turin processors, which top out at 192 cores. AMD also claims that Venice will deliver up to 70 percent higher performance compared to its predecessor, an achievement that stems not just from more cores, but also from significant improvements in per-core efficiency and architectural enhancements. The technological foundation for these gains is TSMC's advanced 2-nanometer manufacturing process. By skipping directly from 4nm to 2nm, AMD can pack more transistors into the same silicon area, boosting both performance and energy efficiency. Memory bandwidth is another area where Venice stands out. The processor will more than double the per-socket memory bandwidth to 1.6 terabytes per second, up from 614 gigabytes per second in the current lineup. This is expected to be achieved through a combination of support for up to 16 channels of DDR5 memory and compatibility with advanced memory technologies such as MR-DIMM and MCR-DIMM. These improvements are critical for feeding data to the large number of high-performance cores, especially in data-intensive workloads common in AI and analytics. AMD is also addressing the growing need for fast communication between CPUs and GPUs. Venice will double the bandwidth for CPU-to-GPU communication, likely by adopting PCI Express 6.0. With up to 128 PCIe lanes, the new platform will be able to move as much as 128 gigabytes of data per second in each direction, not counting encoding overhead. This is particularly important for AI training and inference, where rapid data movement between processors and accelerators is essential. The Venice processor will debut on AMD's new SP7 platform, which is designed to accommodate the increased power and I/O demands of the chip. The SP7 socket is expected to support higher power delivery - potentially well beyond the 700 watts supported by the current SP5 platform - and allow for more compute complex dies on a single package. This new infrastructure will also enable more memory channels and greater expansion capabilities. AMD plans to offer Venice in two main variants: a standard Zen 6 version with up to 96 cores and a high-density Zen 6c version, scaling up to the full 256 cores, both of which support up to 512 threads. Looking ahead, Venice will anchor AMD's Helios rack-scale architecture, which will integrate the new CPUs with next-generation Instinct MI400 GPUs and advanced networking solutions. This system is expected to deliver a substantial leap in AI performance and memory capacity, setting the stage for even more powerful platforms in the years to follow.

[4]

AMD EPYC Venice Server Processor: Up to 256 Zen 6 Cores and 70% Performance Boost

AMD has shared details about its next-generation EPYC server processor, code-named Venice, at the Advancing AI 2025 conference. Expected to launch next year, the Venice processor is built on the new 2nm Zen 6 microarchitecture and will offer up to 256 cores. This core count represents a substantial increase compared to the current Zen 5c-based EPYC processors, which have a maximum of 192 cores. This expanded core count is intended to improve performance for large-scale server workloads and data center applications. One of the key features of Venice is its support for 128 PCIe 6.0 lanes arranged in a dual-channel configuration. This matches previous leaks related to AMD's upcoming SP7 platform. The processor's memory subsystem supports speeds of at least 12,500 MT/s, which is very close to the 12,800 MT/s speed of the second-generation DDR5 MRDIMM memory standard. With 16 memory channels operating at 64 bits each, Venice can deliver up to 1.6 terabytes per second of memory bandwidth. AMD projects a 70% increase compared to the previous generation. When broken down to a per-core basis, this means each Zen 6c core delivers approximately 27.5% better performance than a Zen 5c core. Venice also doubles the bandwidth for communication between the CPU and GPU, which can further accelerate workloads that leverage integrated or discrete GPUs in server systems. These improvements indicate that Venice is designed to address the growing demands of AI, machine learning, and other high-performance computing tasks in data centers.

[5]

AMD confirms next-gen EPYC 'Venice' Zen 6 CPU has 256 cores, will debut in 2026

As an Amazon Associate, we earn from qualifying purchases. TweakTown may also earn commissions from other affiliate partners at no extra cost to you. AMD has confirmed its next-gen Zen 6-based EPYC "Venice" and next-next-gen Zen 7-based EPYC "Verano" CPUs are cooking right now, with up to 256 cores on its upcoming Zen 6-based EPYC "Venice" CPU. During its keynote today at its Advancing AI event, AMD confirmed not only its next-gen EPYC processors but also next-gen Instinct AI series GPU family lineups. AMD launched its new Instinct MI350 series today as well as teasing its next-gen Instinct MI400 series, which will boast HBM4 memory launching in 2026. AMD's upcoming Zen 6-based EPYC "Venice" CPUs will feature two different variants: a standard Zen 6 variant and a denser Zen 6c variant, which will be featured in the SP7 and SP8 sockets, with the former aimed at higher-end solutions, and the latter at entry-level servers. The new platform will feature 16-channel and 12-channel memory support, too. AMD will be fabbing its new EPYC "Venice" CPUs on TSMC's new 2nm process node, offering up to 2x the CPU-to-GPU bandwidth, with a 70% gen-on-gen performance uplift, as well as up to 1.6TB/sec of memory bandwidth. AMD says that it will be using its new Zen 6-based EPYC "Venice" CPUs, new Instinct MI400 series AI GPUs, and Vulcano FPGAs inside of its new Helios data center racks in 2026.

[6]

AMD confirms next-next-gen Zen 7-based EPYC 'Verano' CPUs and Instinct MI500 AI GPUs for 2027

As an Amazon Associate, we earn from qualifying purchases. TweakTown may also earn commissions from other affiliate partners at no extra cost to you. AMD has confirmed its next-next-gen Zen 7-based EPYC "Verano" CPUs and Instinct MI500 series AI accelerators will both be launching for next-gen AI racks in 2027. AMD held its Advancing AI event earlier today, unveiling its new Zen 6-based EPYC "Venice" CPUs with up to 256 cores and 512 threads of processing power, as well as its new Instinct MI350 series AI accelerators, on top of teasing its next-gen Instinct MI400 series AI chips that will boast 10x the performance of its just-released MI350 series, with MI400 AI chips boasting up to 432GB of next-gen HBM4 memory. The company surprisingly introduced its next-next-gen Zen 7-based EPYC "Verano" CPUs and Instinct MI500 series AI chips, where we should expect the new EPYC "Verano" chips to use the new Zen 7 architecture (but AMD didn't confirm this part). The new EPYC Verano and Instinct MI500 series chips will power the next-gen wave of AI server racks from the company, as it will be using its just-announced EPYC Venice and Instinct MI400 series chips inside of its new Helios AI servers. Speaking of AMD's next-gen Zen 7 processors, we had a new leak yesterday that teased that the consumer versions of Zen 7 will be on the new AM6 socket, offering up to 32 cores and 64 threads of next-gen Zen 7-based CPU performance on desktop PCs in the future. MLID's sources said that there will be "tons" of V-Cache on the Zen 7 desktop chips, something that I'm sure we're ALL looking forward to.

[7]

AMD Confirms Next-Gen EPYC Venice "Zen 6" CPUs With 256 Cores In 2026, EPYC Verano "Zen 7" CPUs & Instinct MI500 GPUs For 2027

AMD has confirmed its next-gen product lineups, including Zen 6-based EPYC Venice, Zen 7-based EPYC Verano, and Instinct MI500 series. AMD EPYC Venice With Zen 6 In 2026 & EPYC Verano With Zen 7 In 2027, Up To 256 Cores Next Year With Instinct MI500 Series For Next-Gen Rack In 2027 Wrapping up its Advancing AI keynote, AMD confirmed its next-generation EPYC and Instinct family lineups. During its keynote, AMD confirmed that next year, it will be introducing its Instinct MI400 series which offers a 10x performance uplift over the MI350 series that launched today. In addition to that, the company is also announcing some key details of its next-generation EPYC lineup that is codenamed "Venice". The lineup will incorporate the brand-new Zen 6 architecture that debuts next year and features up to 256 cores. Based on previous reports, AMD's 6th Gen EPYC Venice CPUs will come in two flavors, just like the Zen 5 and Zen 4 offerings, a standard Zen 6 variant and a denser Zen 6C variant. These will be featured in the SP7 and SP8 sockets, with the former being the higher-end solution while the latter aims at the entry-level server solutions. The platform will come with both 16 & 12-channel memory support. In terms of core counts, the AMD EPYC 9006 "Venice" CPUs will have up to 96 cores and 192 threads with up to 8 CCDs in classic configurations, while Zen 6C variants will scale up to 256 cores and 512 threads. The chips will be fabricated on TSMC's 2nm process node and offer up to 2x the CPU-to-GPU bandwidth with a 70% gen-on-gen performance gain and up to 1.6 TB/s of memory bandwidth. The AMD EPYC Venice CPUs, Instinct MI400 series and Vulcando FPGAs will be packed within the Helios data center rack in 2026. In 2027, AMD will be introducing its next-gen EPYC Verano CPUs and Instinct MI500 series. The EPYC Verano CPUs are likely going to utilize the Zen 7 core architecture since AMD is shifting to an annual cadence, so we are going to see updates on the datacenter and AI front at a very rapid pace, similar to what NVIDIA is doing now with a standard and an "Ultra" offering. These will be used to power the next-gen AI racks and will offer a disruptive uplift in overall performance.

Share

Share

Copy Link

AMD reveals its roadmap for advanced AI computing solutions, including the EPYC 'Venice' CPU with 256 cores and significant performance improvements, set to launch in 2026, followed by the next-generation 'Verano' CPU and MI500X GPU in 2027.

AMD's Next-Generation AI Computing Solutions

AMD has unveiled its ambitious roadmap for advanced AI computing solutions, showcasing a series of innovations set to debut in 2026 and 2027. The company's plans focus on enhancing performance, efficiency, and scalability in data center and AI applications

1

.EPYC 'Venice': A Leap in Server CPU Technology

At the heart of AMD's 2026 lineup is the EPYC 'Venice' processor, built on the Zen 6 architecture using TSMC's 2nm process technology

2

. Key features include:

Source: Guru3D

- Up to 256 high-performance Zen 6 cores, a 33% increase from the current generation

- 70% performance improvement over the existing EPYC 'Turin' processors

- Doubled CPU-to-GPU bandwidth, likely utilizing PCIe 6.0 interface

- More than doubled per-socket memory bandwidth, reaching 1.6 TB/s

- Support for advanced memory modules like MR-DIMM and MCR-DIMM

The Venice CPU will be available in two variants: a standard Zen 6 version with up to 96 cores and a high-density Zen 6c version scaling up to 256 cores

3

.Enhanced Memory and I/O Capabilities

Venice's memory subsystem supports speeds of at least 12,500 MT/s, approaching the 12,800 MT/s speed of second-generation DDR5 MRDIMM memory. With 16 memory channels operating at 64 bits each, Venice can deliver up to 1.6 terabytes per second of memory bandwidth

4

.The processor will feature 128 PCIe 6.0 lanes in a dual-channel configuration, significantly enhancing I/O capabilities for data-intensive workloads

4

.Helios: AMD's First In-House Designed Rack-Scale AI System

Source: TweakTown

Venice will be a key component of AMD's Helios rack-scale system for AI, which will also include:

- Instinct MI400X-series accelerators, projected to double AI inference performance

- Pensando 'Vulcano' 800 GbE network cards compliant with the UEC 1.0 specification

1

Related Stories

Looking Ahead: 2027 AI Plans

AMD is already developing its 2027 rack-scale solution, which will include:

- EPYC 'Verano' processors

- Instinct MI500X-series accelerators

- Pensando 'Vulcano' 800 GbE NICs

1

Source: Tom's Hardware

While specific details are not yet available, AMD CEO Lisa Su hinted at further improvements in performance, efficiency, and scalability .

Impact on AI and Data Center Computing

These advancements signify AMD's commitment to meeting the growing demands of AI, machine learning, and high-performance computing tasks in data centers. The increased core count, improved memory bandwidth, and enhanced CPU-to-GPU communication are designed to accelerate complex AI workloads and large-scale server applications

3

.As AMD continues to innovate in this space, the competition in the AI hardware market is likely to intensify, potentially leading to more rapid advancements in AI computing capabilities across the industry.

References

Summarized by

Navi

[2]

[3]

Related Stories

AMD Unveils Zen 6 and Zen 7 CPU Roadmap: 2nm Process Technology and Enhanced AI Capabilities Coming in 2026-2027

11 Nov 2025•Technology

AMD unveils Helios rack-scale AI system with 72 MI455X accelerators and 256-core EPYC Venice

06 Jan 2026•Technology

AMD Launches 5th Gen EPYC 'Turin' CPUs with Up to 192 Cores and 5 GHz Clock Speeds

11 Oct 2024•Technology

Recent Highlights

1

AI chatbots validate you too much, making you less kind to others, Stanford study reveals

Science and Research

2

Anthropic's Claude Code Source Leak Reveals Hidden AI Agent Plans and Extensive System Access

Technology

3

Judge blocks Pentagon from branding Anthropic a security risk over AI safety guardrails dispute

Policy and Regulation