AI agent designs complete RISC-V CPU from scratch in 12 hours using autonomous workflow

2 Sources

2 Sources

[1]

AI agent designs a complete RISC-V CPU from a 219-word spec sheet in just 12 hours -- comparably simple design required 'many tens of billions of tokens'

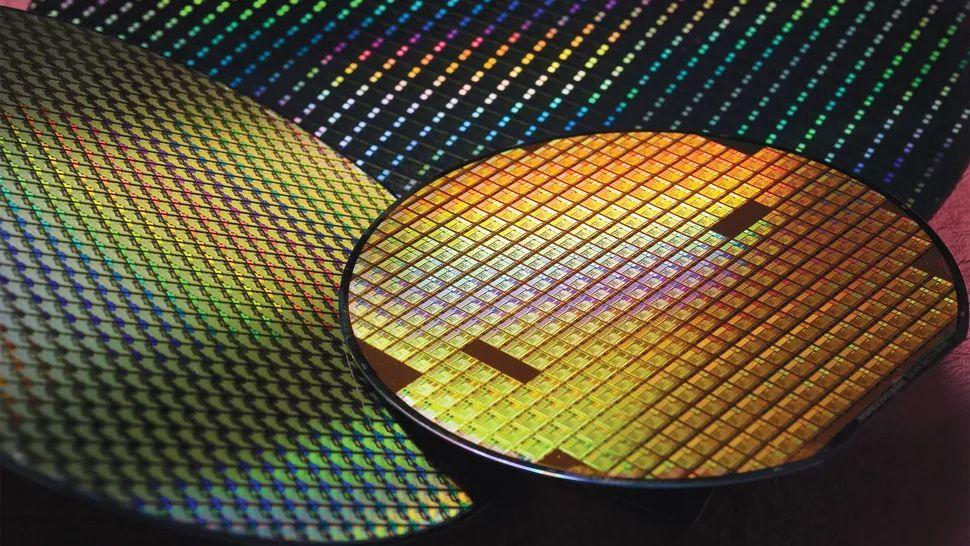

AI chip design startup Verkor.io claims, in a research paper published in March, that its agentic AI system, Design Conductor, autonomously produced a complete RISC-V CPU core -- taking a 219-word requirements document and generating a verified, layout-ready design in 12 hours, which is orders of magnitude faster than the standard 18- to 36-month timelines seen in commercial chip design. This is the first time an autonomous agent has built a working CPU from spec to GDSII layout file, according to Verkor. The resulting processor -- VerCore -- is a five-stage pipelined, in-order, single-issue core that met timing at 1.48 GHz on the ASAP7 7nm process design kit, scoring 3,261 on the CoreMark benchmark. Verkor's paper goes into detail on the pipeline architecture, which includes instruction fetch, decode, execute, memory, and writeback stages with early branch resolution and operand forwarding. During optimization, the system independently implemented a fast Booth-Wallace multiplier that clocked at 2.57 GHz and a one-cycle branch penalty design that the agent selected after implementing and testing both one-cycle and two-cycle variants. Verkor compares VerCore's CoreMark performance to Intel's Celeron SU2300, a 2011 mobile chip based on the Penryn architecture. A five-stage in-order core with no caches and no out-of-order execution is a fairly straightforward design by industry standards. Verkor's own paper notes that leading-edge chips cost north of $400 million and take 18 to 36 months with engineering teams in the hundreds, but VerCore is far simpler than those designs. That said, the 12-hour timeline is still notable for a fully autonomous run from spec to layout, even if it did require "many tens of billions of tokens" at this comparatively pale level of complexity. VerCore hasn't been physically fabricated and was instead verified in simulation using Spike, a reference RISC-V ISA simulator, and ASAP7 is an academic process design kit, not a production 7nm node. Verkor says it can run a uCLinux variant in simulation. Verkor's paper is candid about the limitations of the underlying language models, admitting that the agent sometimes "underestimates the complexity of work that is required to address certain issues." For example, in one case, when failing to meet timing, Design Conductor tried to make major changes to "deepen the pipeline, instead of looking for simpler explanations." In another case, the researchers observed the model reasoning about Verilog, an event-driven language, as if it were sequential code. "While we found that this did not impact DC's ability to achieve functional correctness, it made it more challenging for DC to debug timing issues," the researchers explained. The researchers estimate that five to 10 human experts will still be required to guide the system toward a production-ready chip. In addition, compute requirements grow non-linearly as design complexity increases, which makes the whole process less practical on a commercial scale. Verkor said it plans to release VerCore's RTL source and build scripts by the end of April, and the company also intends to showcase an FPGA implementation at DAC (the annual Electronic Design Automation Conference). Previous AI chip design efforts, such as the Chinese researchers who produced a RISC-V CPU in under five hours in 2023 and the more recent QiMeng project, used different methodologies and architectures. Verkor's Design Conductor handles the full design process from spec to GDSII autonomously, though it shares the same limitation that all other AI-designed chips have: no physical silicon. Follow Tom's Hardware on Google News, or add us as a preferred source, to get our latest news, analysis, & reviews in your feeds.

[2]

An AI agent just designed a complete RISC-V CPU from scratch in 12 hours

Serving tech enthusiasts for over 25 years. TechSpot means tech analysis and advice you can trust. In brief: An agentic AI system has reportedly designed a complete RISC-V CPU core from scratch in just 12 hours, marking the first time an autonomous agent has built a working CPU from specification to GDSII. Like human engineers, the AI agent followed the conventional design cycle - design, build, test, and refine - but did so entirely on its own rather than relying on separate automation tools for each stage. The processor - dubbed VerCore - was created by chip design startup Verkor.io using its agentic AI system, Design Conductor. According to a whitepaper published by the company, VerCore features a five-stage pipeline design with an in-order, single-issue architecture and a 1.48GHz clock speed. The chip reportedly scored 3,261 on the CoreMark benchmark, a specialized tool used to measure the performance of microcontrollers and CPUs in embedded systems. The modest score suggests that VerCore can barely keep pace with an entry-level Intel Celeron SU2300 from mid-2011, indicating that the new design is unlikely to compete with modern CPUs. It is worth noting that Design Conductor is not itself an AI model, but a harness tool that constrains large language models to follow a specific set of instructions in pursuit of a defined objective. In this case, it worked autonomously with a 219-word specification document provided by the VerCore engineers and produced a GDSII file that can be used to fabricate an actual CPU core using EDA software. A major caveat worth noting is that VerCore has not yet been physically fabricated; it has only been validated in simulation using the reference RISC-V ISA simulator, Spike. Its layout was designed using ASAP7 PDK, an open-source academic design kit that models a 7nm-class process node. The predictive PDK was developed by engineers at Arizona State University in collaboration with ARM Research and is available on GitHub under the BSD 3-Clause license. Verkor plans to release all relevant design files by the end of this month, allowing hardware designers and third-party engineers to verify the company's claims. The company also plans to showcase an FPGA implementation of VerCore at the Design Automation Conference in Long Beach, California, in July. This is not the first time AI has been used for digital hardware synthesis. In 2020, a fine-tuned GPT-2 model dubbed DAVE was trained on Verilog code to generate simple hardware logic circuits. This was followed in 2023 by an 8-bit processor layout reportedly designed entirely by GPT-4. As of 2026, most leading large language models are capable of designing and testing chips with basic functionality, albeit with varying levels of reliability.

Share

Share

Copy Link

Chip design startup Verkor.io claims its agentic AI system, Design Conductor, autonomously produced a complete RISC-V CPU core in just 12 hours—a process that typically takes 18 to 36 months. The resulting VerCore processor achieved 1.48 GHz on a 7nm process and scored 3,261 on CoreMark, though it remains unverified in physical silicon.

AI Agent Designs CPU in Record Time

Chip design startup Verkor.io has achieved what it claims is a first in AI chip design: an autonomous agent that built a working RISC-V CPU from specification to GDSII layout file in just 12 hours

1

. The agentic AI system, called Design Conductor, took a 219-word requirements document and generated a verified, layout-ready design—a process that typically requires 18 to 36 months with engineering teams numbering in the hundreds1

. This marks the first time an AI agent designs CPU hardware through the complete conventional design cycle—design, build, test, and refine—entirely on its own rather than relying on separate automation tools for each stage2

.The resulting processor, dubbed VerCore, features a five-stage pipeline design with instruction fetch, decode, execute, memory, and writeback stages, incorporating early branch resolution and operand forwarding

1

. The in-order, single-issue core achieved timing at 1.48 GHz on the ASAP7 7nm process design kit and scored 3,261 on the CoreMark benchmark—performance comparable to Intel's Celeron SU2300, a 2011 mobile chip based on the Penryn architecture1

2

.

Source: TechSpot

How Design Conductor Works

Design Conductor is not itself an AI model but a harness tool that constrains large language models to follow specific instructions in pursuit of a defined objective

2

. During optimization, the system independently implemented a fast Booth-Wallace multiplier that clocked at 2.57 GHz and selected a one-cycle branch penalty design after implementing and testing both one-cycle and two-cycle variants1

. The autonomous hardware design process required "many tens of billions of tokens" even for this comparatively simple design1

.Verkor.io's research paper candidly acknowledges limitations in the underlying language models. The agent sometimes "underestimates the complexity of work that is required to address certain issues," such as attempting to deepen the pipeline architecture instead of seeking simpler explanations when failing to meet timing

1

. Researchers also observed the model reasoning about Verilog, an event-driven language, as if it were sequential code, which complicated debugging timing issues though it didn't impact functional correctness1

.

Source: Tom's Hardware

Related Stories

Practical Limitations and Future Outlook

A critical caveat remains: VerCore has not been physically fabricated and was instead verified in simulation using Spike, a reference RISC-V ISA simulator

1

2

. ASAP7 is an academic process design kit developed by Arizona State University in collaboration with ARM Research, not a production 7nm node2

. Verkor says the design can run a uCLinux variant in simulation1

.The researchers estimate that five to 10 human experts will still be required to guide the system toward a production-ready chip

1

. Additionally, compute requirements grow non-linearly as design complexity increases, which makes the process less practical on a commercial scale for leading-edge chips that cost north of $400 million1

. Verkor.io plans to release VerCore's RTL source and build scripts by the end of April and showcase an FPGA implementation at the Design Automation Conference (DAC) in Long Beach, California, in July1

2

. This transparency will allow hardware designers and third-party engineers to verify the company's claims and assess whether AI-driven Electronic Design Automation (EDA) workflows can scale beyond academic demonstrations to address real-world production challenges.References

Summarized by

Navi

[1]

Related Stories

Recent Highlights

1

OpenAI releases GPT-5.5, advancing toward AI superapp with enhanced coding and research tools

Technology

2

Sony AI's robot beats elite table tennis players, signals new era for physical AI

Science and Research

3

SpaceX strikes deal with Cursor, secures option to buy AI coding startup for $60 billion

Technology